Mô tả:

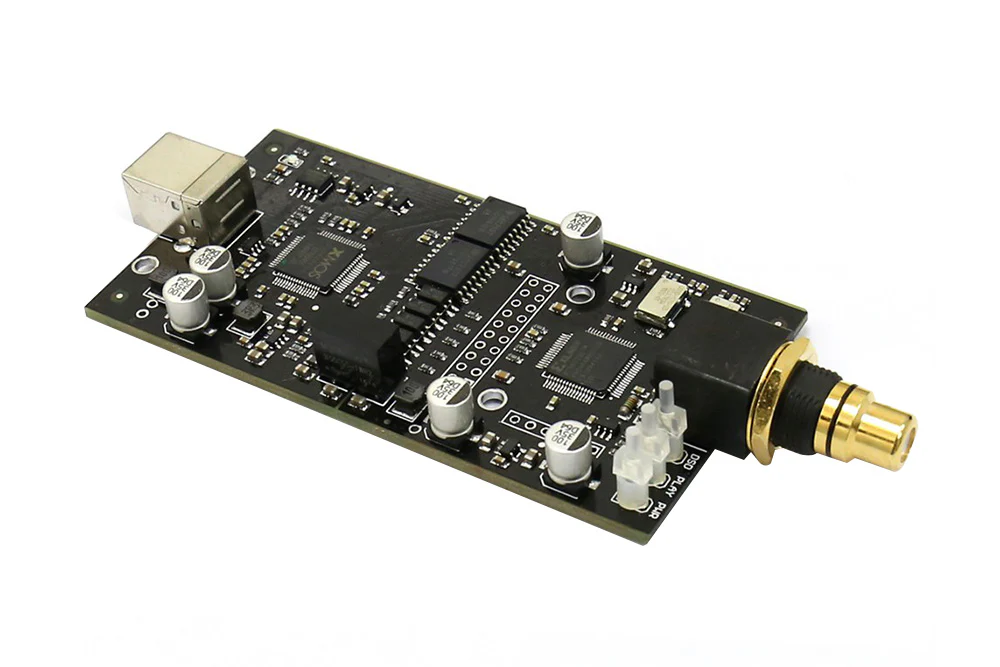

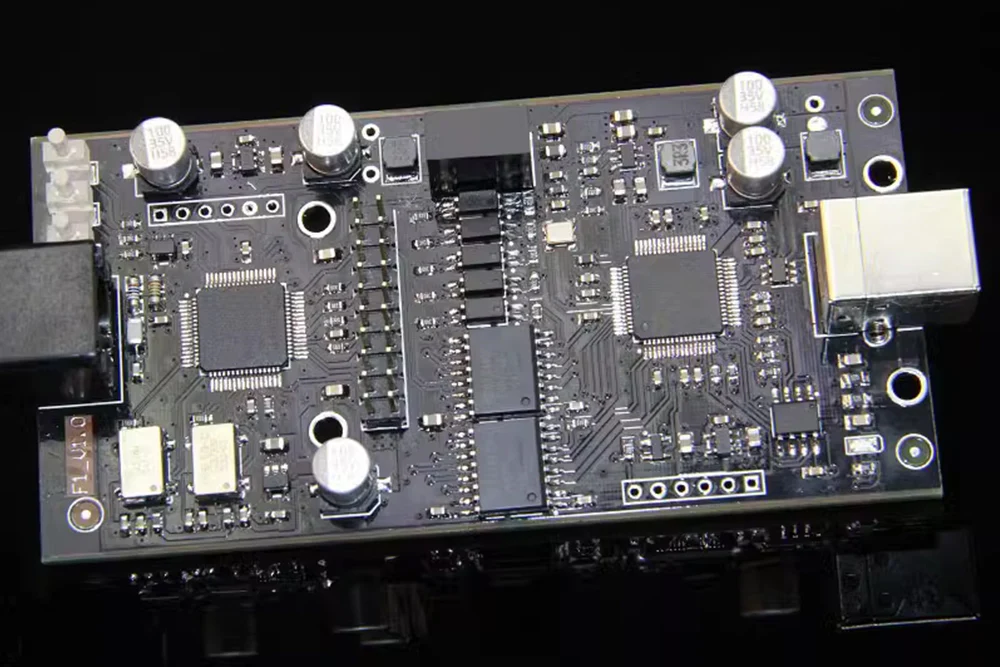

F-1 là giao diện âm thanh số USB hiệu năng cao do đội ngũ chúng tôi phát triển, sử dụng chip dòng xCORE-200 mới nhất của XMOS. F-1 sử dụng hệ thống clock jitter thấp cho giao diện số. Thiết bị dùng chuẩn đầu vào USB 2.0.

Chip XMOS thế hệ mới XU208 áp dụng công nghệ sản xuất tiên tiến hơn, hiệu năng gấp đôi chip U8 cũ, đạt khả năng xử lý 1000 MIPS.

- F-1 là sản phẩm đầu tiên sử dụng giao diện USB với chip XMOS xCORE-200 mới nhất. Chip thế hệ mới với công nghệ tiên tiến, hiệu năng gấp đôi chip U8, đạt 1000 MIPS.

- Như đã biết, xử lý âm thanh số đòi hỏi thuật toán nặng. Đội ngũ chúng tôi có nhiều năm kinh nghiệm trong lĩnh vực audio số, đồng thời nhận được hỗ trợ từ đội ngũ FAE của XMOS, đã thực hiện nhiều cải tiến kỹ thuật và tối ưu thuật toán dựa trên firmware gốc.

Thông số kỹ thuật:

Tần số lấy mẫu hỗ trợ trên từng đầu ra:

- PCM:

44.1KHz, 48KHz, 88.2KHz, 96KHz

176.4KHz, 192KHz, 352.8KHz, 384KHz

→ Trong đó:

- I2S hỗ trợ đầy đủ các mức sample rate

- S/PDIF hỗ trợ tối đa 192KHz

- DSD:

2.8 MHz (DSD64) – DoP, native

5.6 MHz (DSD128) – DoP, native

11.2 MHz (DSD256) – native

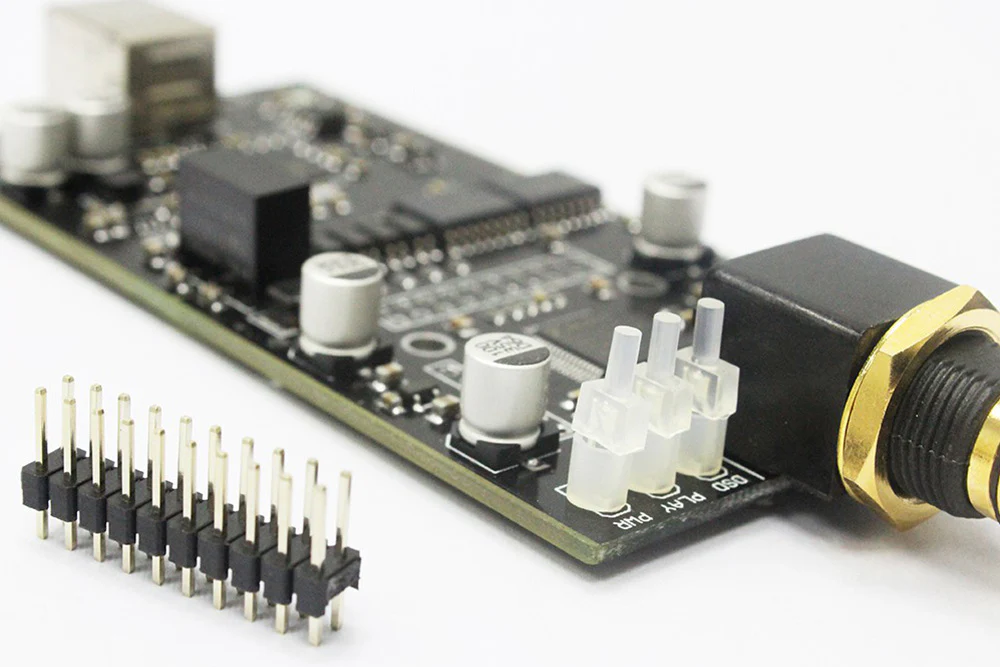

Chuẩn điện của các giao diện:

- Cổng USB đầu vào là loại USB-B tiêu chuẩn (cổng cái), nguồn cấp USB từ 4.5V–5.1V

- Cổng RCA xuất S/PDIF:

- Mức điện áp 550mV (theo tải chuẩn)

- Trở kháng đầu ra: 75 ohm

Chi tiết thiết kế:

- Áp dụng triết lý “nguồn điện là nền tảng của âm thanh”, chú trọng thiết kế mạch cấp nguồn. Sử dụng LDO hiệu năng cao, nhiễu thấp, phản hồi nhanh làm nguồn chính. Toàn bộ mạch dùng 2 LDO độc lập; phần clock sử dụng LDO siêu nhiễu thấp của ADI để đảm bảo hiệu năng tối đa.

- PCB sử dụng thiết kế 4 lớp, đảm bảo mặt phẳng mass và nguồn đầy đủ. Áp dụng phương pháp thiết kế số tốc độ cao để đảm bảo toàn vẹn tín hiệu và nguồn. Tín hiệu clock được xử lý đặc biệt với thiết kế đóng gói và kiểm soát trở kháng chính xác, giúp nâng cao chất lượng tín hiệu và khả năng chống nhiễu.

- Tín hiệu USB tốc độ cao sử dụng trở kháng vi sai 90 ohm

Tương thích hệ thống:

- Windows 7, Windows 8 (32/64-bit) – cần cài driver

- macOS 10.6 trở lên – dùng driver sẵn

- Linux (kernel hỗ trợ UAC2) – dùng driver sẵn

- Android 4.2 trở lên – cần hỗ trợ OTG

Mô tả chân tín hiệu I2S:

- Mức mute cao (High dB mute); khi DSD ON sẽ là luồng dữ liệu DSD

- Tất cả tín hiệu ở mức LVCMOS, điện áp 3.3V

- VD3.3 là nguồn cấp đầu ra, dòng tối đa 50mA

- MCLK xuất clock 22.5792MHz hoặc 24.576MHz

- FS0, FS1, FS2 là các bit chọn sample rate (FS3 không dùng)

- LRCLK = DSDR, SDATA = DSDL, BCLK = DCLK

Đang cập nhật

Đang cập nhật

.png)